反激開關電源環路設計優化方案

在開關電源設計領域,AC-DC 環路布局對電源系統的性能有著決定性影響,其合理性直接關聯到電源的效率、電磁兼容性以及穩定性和可靠性。以下將分別從隔離電源方案與非隔離電源方案兩個角度,詳細闡述反激開關電源環路設計的關鍵要點。

一、隔離電源方案

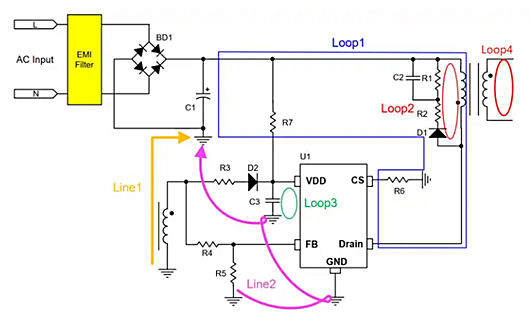

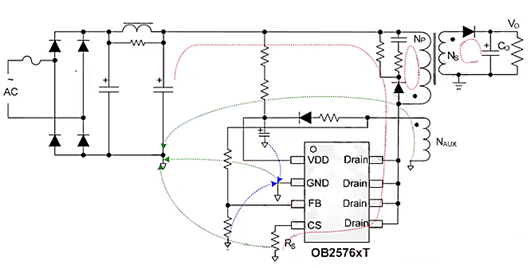

以常見的反激式原邊控制電源為例,其典型應用原理圖包含 4 個主要環路:

原邊主功率環路(Loop1) :此環路的面積大小對電源的效率和電磁干擾水平有著顯著影響。在設計布局時,應盡可能縮小環路面積,同時將走線加粗,以降低線路電阻,減少能量損耗,從而優化電源的轉換效率。

RCD 吸收環路(Loop2) :同樣需要控制環路面積,避免過大的環路引發電磁干擾等問題,確保電路的穩定運行。

VDD 環路(Loop3) :在該環路中,VDD 電容 C3 的布局位置至關重要,必須緊貼芯片放置,以減少引線電感和電阻,保障芯片供電的穩定性,進而提升整個電源系統的可靠性。

Vout 環路(Loop4) :其設計也應遵循環路面積最小化原則,以降低電磁干擾,維持輸出電壓的穩定性。

在 GND 走線設計方面,輔助繞組應直接連接到輸入電容的地,以減少地回路的阻抗,降低干擾。VDD 電容 C3 及 FB 下阻 R5 應先連接到芯片的 GND 管腳,再連接到輸入電容的地,這樣的布局方式有助于優化電路的接地性能,提高信號的穩定性和準確性。

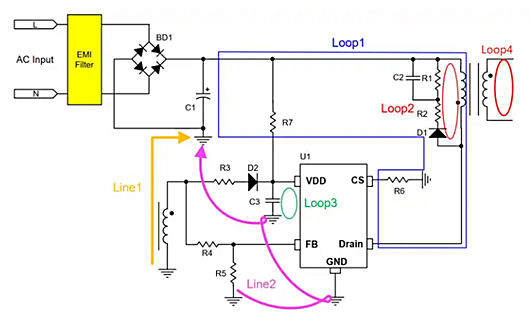

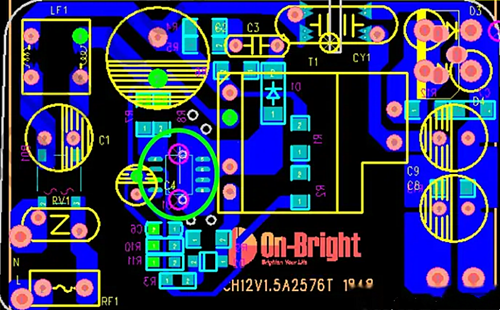

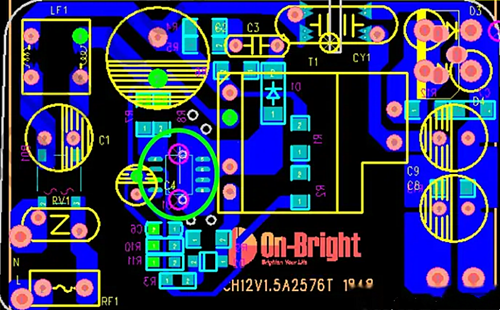

以 OB2576XT 為例,其原理圖及布局設計建議如下:

二、非隔離電源方案

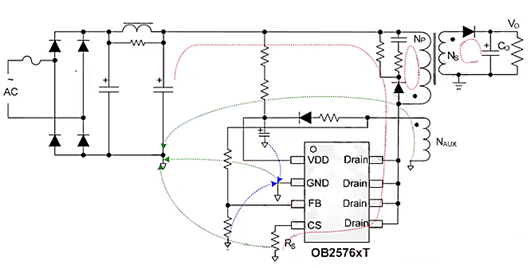

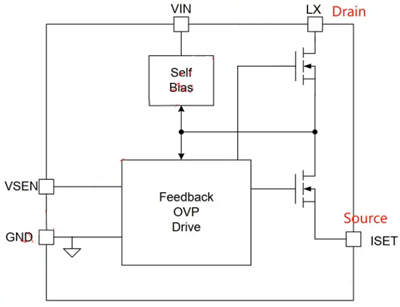

非隔離方案的典型應用原理圖中有兩個關鍵環路:

源開關環路(Loop1) :在 Layout 時,要嚴格控制環路面積,使其盡可能小,以降低電磁干擾的產生。同時,在滿足環路面積要求的前提下,功率電感 L3 應盡量遠離母線上的 π 濾波電路,避免相互干擾,影響電源的性能。

續流環路(Loop2) :同樣遵循環路面積最小化原則,以提高電源的效率和穩定性。

此外,反饋電阻 R4 和 R3 應靠近芯片引腳放置,以減少信號傳輸的損耗和干擾,提高反饋信號的準確性。芯片的旁路電容也應靠近芯片引腳放置,以提供穩定的電源供應,抑制高頻噪聲,保障芯片的正常工作。

在該轉換電路中,LX(Drain)作為主電源的 DC 定點,可在電流主回路走線上增加敷銅面積,以改善電源的散熱性能,提升其工作效率和可靠性。ISET(SOURSE)是電源的開關動點,應盡量縮短 SOURCE 和功率電感間的線徑,從而有效改善 EMI 特性,降低電磁干擾對系統的影響。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280